隨著人工智能、高性能計算(HPC)和5G/6G網(wǎng)絡的飛速發(fā)展,對芯片性能、集成度和能效的要求達到了前所未有的高度。在這一背景下,CoWoS(Chip-on-Wafer-on-Substrate) 作為一種先進的2.5D/3D封裝技術,已成為支撐下一代計算與通信硬件發(fā)展的關鍵基石。它不僅是一種封裝工藝,更是系統(tǒng)級架構創(chuàng)新的核心體現(xiàn),深刻影響著從芯片設計到網(wǎng)絡基礎設施的整個技術開發(fā)生態(tài)。

一、CoWoS封裝技術核心特點

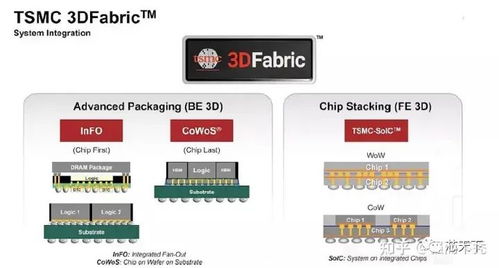

CoWoS技術由臺積電(TSMC)主導開發(fā),其核心在于將多個異構芯片(如邏輯芯片、高帶寬內存HBM等)通過硅中介層(Silicon Interposer)集成在一個封裝內,再連接到基板上。其主要特點包括:

- 異構集成與系統(tǒng)級封裝(SiP): CoWoS最顯著的特點是實現(xiàn)了真正的異構集成。它允許將不同工藝節(jié)點、不同功能(如CPU、GPU、AI加速器、HBM)的芯片集成在同一個封裝內。這種“芯片即系統(tǒng)”的理念,打破了傳統(tǒng)單芯片(SoC)在面積、工藝兼容性和內存帶寬上的限制。

- 硅中介層(Silicon Interposer)的關鍵作用: 硅中介層是CoWoS技術的核心組件。它本質上是一塊擁有超高密度互連(通過硅通孔TSV和微凸塊實現(xiàn))的硅片。其特點包括:

- 超高互連密度與帶寬: 相比傳統(tǒng)有機基板,硅中介層上的布線線寬和間距可以達到微米級,能夠提供數(shù)千甚至上萬個互連接點,從而實現(xiàn)芯片間超高速、低延遲的數(shù)據(jù)傳輸。這是實現(xiàn)HBM與邏輯芯片間超高帶寬(如超過1TB/s)的基礎。

- 優(yōu)異的電學與熱學性能: 硅材料的特性使得信號傳輸損耗低、電氣性能穩(wěn)定,同時其良好的導熱性有助于封裝整體的散熱管理。

- 2.5D向3D的演進: CoWoS本身是2.5D封裝(芯片并排放置在硅中介層上),但其技術與3D IC技術(如SoIC)緊密結合,正在向更立體的3D堆疊方向發(fā)展,實現(xiàn)芯片間的垂直互連,進一步縮短互連長度,提升性能和能效。

二、CoWoS封裝技術的核心優(yōu)勢

CoWoS技術的優(yōu)勢直接回應了現(xiàn)代高性能計算和網(wǎng)絡技術的核心挑戰(zhàn):

- 突破“內存墻”與“功耗墻”: 通過將HBM與計算芯片緊耦合集成,實現(xiàn)了超高的內存帶寬和極低的數(shù)據(jù)存取延遲,有效緩解了制約計算性能的“內存墻”問題。短距離、高能效的互連降低了數(shù)據(jù)傳輸功耗,助力應對“功耗墻”。

- 提升系統(tǒng)性能與能效比(Performance per Watt): 異構集成優(yōu)化了數(shù)據(jù)流路徑,減少了芯片外通信的開銷。將關鍵部件封裝在一起,降低了I/O驅動功耗和信號延遲,整體系統(tǒng)能效比顯著提升,這對于數(shù)據(jù)中心和邊緣計算設備至關重要。

- 提高集成度與縮小系統(tǒng)尺寸: 在單個封裝內集成多顆芯片,極大地提高了功能密度,使最終產(chǎn)品(如服務器、網(wǎng)絡交換機、AI訓練卡)更加緊湊,滿足了對設備小型化和高計算密度的需求。

- 設計靈活性與縮短上市時間: 采用Chiplet(芯粒)設計范式,開發(fā)者可以像搭積木一樣,將不同工藝、不同功能的已驗證芯粒(如采用成熟工藝的I/O芯片和采用先進工藝的計算核心)通過CoWoS集成,降低了大規(guī)模單芯片的設計復雜度和風險,加速了產(chǎn)品迭代。

三、在計算機軟硬件及網(wǎng)絡技術開發(fā)中的關鍵應用與影響

CoWoS技術已不僅僅是制造工藝,它正在重塑軟硬件開發(fā)的范式:

在硬件開發(fā)層面:

- AI與HPC芯片: 英偉達(NVIDIA)的H100、B200,AMD的MI300等頂級AI加速器和GPU均采用CoWoS封裝集成HBM,是其強大算力的物理基礎。

- 高端CPU: 英特爾、AMD的高端服務器CPU也利用類似2.5D封裝技術集成大容量緩存或多個計算核心。

- 網(wǎng)絡與交換芯片: 在高速網(wǎng)絡交換機、DPU(數(shù)據(jù)處理單元)中,CoWoS技術用于集成高速SerDes(串行器/解串器)和核心處理單元,以滿足400G/800G乃至更高以太網(wǎng)端口對帶寬和密度的苛刻要求。

在軟件開發(fā)與系統(tǒng)架構層面:

- 驅動新的編程模型: 硬件的高度集成化(如內存與計算的緊耦合)要求軟件棧(如編譯器、運行時庫、框架)進行相應優(yōu)化,以充分發(fā)揮硬件潛力。例如,需要開發(fā)能感知NUMA(非統(tǒng)一內存訪問)但更極端的“芯片內”內存層次結構的編程模型。

- 影響系統(tǒng)架構設計: 在數(shù)據(jù)中心和網(wǎng)絡架構中,搭載CoWoS芯片的服務器和交換機節(jié)點具備更強的單體處理能力,這促使網(wǎng)絡拓撲(如更注重低延遲的NVLink網(wǎng)絡、葉脊架構)、存儲架構和任務調度策略發(fā)生變革,向更分布式、更均衡的方向發(fā)展。

在網(wǎng)絡技術開發(fā)層面:

- 支撐高速互聯(lián): CoWoS封裝的芯片是構建超高性能網(wǎng)絡設備(如智能網(wǎng)卡、交換路由器)的核心,直接支撐了數(shù)據(jù)中心內部(東西向流量)和外部(南北向流量)的Tb級數(shù)據(jù)傳輸需求,為云服務、邊緣計算和未來6G網(wǎng)絡提供底層硬件保障。

- 促進網(wǎng)絡功能虛擬化(NFV)與軟件定義網(wǎng)絡(SDN): 強大的封裝芯片使得單臺設備能承載更復雜、更密集的網(wǎng)絡功能虛擬化實例,提升了網(wǎng)絡靈活性和資源利用率。

結論

CoWoS封裝技術通過其革命性的異構集成能力,已成為驅動后摩爾時代計算性能持續(xù)增長的關鍵引擎。它不僅僅是一項半導體制造技術,更是連接先進芯片設計、高效能系統(tǒng)構建和下一代網(wǎng)絡基礎設施的橋梁。隨著Chiplet生態(tài)的成熟和3D集成技術的進一步發(fā)展,CoWoS及其衍生技術將繼續(xù)在人工智能、高性能計算、高速網(wǎng)絡等前沿領域扮演不可或缺的角色,深刻定義未來十年計算機軟硬件及網(wǎng)絡技術的開發(fā)格局。對于開發(fā)者、架構師和決策者而言,深入理解CoWoS的特點與優(yōu)勢,是把握未來技術浪潮、進行前瞻性產(chǎn)品與系統(tǒng)設計的重要前提。